| 제목 | [산업분석] 반도체분야_반도체 소부장의 공식 |

|---|

| 분류 | 성장동력산업 | 판매자 | 강정훈 | 조회수 | 658 | |

|---|---|---|---|---|---|---|

| 용량 | 5.68MB | 필요한 K-데이터 | 11도토리 |

| 파일 이름 | 용량 | 잔여일 | 잔여횟수 | 상태 | 다운로드 |

|---|---|---|---|---|---|

| 5.68MB | - | - | - | 다운로드 |

| 데이터날짜 : | 2023-04-18 |

|---|---|

| 출처 : | 증권사 |

| 페이지 수 : | 101 |

< 목 차 >

1. Summary

2. 전방 투자 대비 떨어지는 생산 효율

3. 소부장 업체의 구조적 성장은 확정적

4. 반도체 공정 Flow 및 주요 Supply chain

5. 투자 Theme

6. 기업 분석

리노공업(BUY, 20 만원)

ISC(BUY, 5.5 만원)

유니셈(BUY, 1.2 만원)

대덕전자(BUY, 3.4 만원)

에스앤에스텍(NR)

레이크머티리얼즈(NR)

원익머트리얼즈(NR)

케이엔제이(NR)

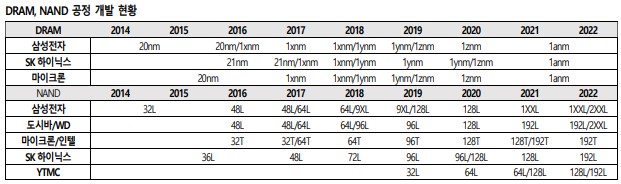

전공정 기술 개선이 어려워지고, 앞으로 더 어려워질 전망이다. 인텔이 주장해 온 무어 의 법칙은 이미 2010 년 초반부터 깨졌다. DRAM 은 Capacitor 의 A/R(Aspect Ratio, 종횡비) 때문에 첨단 공정 도입에 따른 원 가 개선율이 확연하게 둔화되었다. Capacitor 의 종횡비 문제는 EUV 로 해결할 수 없다. 종횡비가 높아질수록 Capacitor 의 형성이 어려워지고, 형성 이후에도 쓰러질 확률이 높아진다. Capacitor 의 종횡비는 기하급수적으로 상승하고 있으며, DRAM 공정난이도 는 Capacitor 의 종횡비에 비례한다. 실제로 DRAM 업체들은 1anm 전환 과정과 1bnm 개발 과정에서 큰 어려움을 겪고 있다. NAND 도 2D NAND 의 한계를 피해 3D NAND 전환에 성공했으나, 3D NAND 에 서도 적층 단수가 증가함에 따라 DRAM 과 마찬가지로 A/R 문제에 노출될 수 밖에 없다. 실제로 NAND 업체들은 200 단 내외 공정 개발에 오랜 시간을 소요하고 있다.

그리고 비메모리 Foundry 는 기존 FinFET(Fin Field Effect Transistor)을 GAAFET (Gate All Around FET) 공정으로 전환하는 과정에서 기술 난이도가 대폭 상승하고 있 다. Transistor 의 선폭이 좁아지면, 누설전류(Leakage Current)가 발생하여 Short Channel Effect 가 발생한다. 14nm 선폭부터 적용되어 온 FinFET 공정이 4nm 미만 선 폭에서는 한계를 보일 것으로 판단된다. 그래서 Foundry 업체들은 4nm 미만 선폭에서 GAA(Gate All Around) 공정을 적용할 계획이다. 삼성전자는 3nm 선폭부터, TSMC 는 2nm 부터 GAA 공정을 적용할 계획이다. GAA 는 Transistor 구조를 전면적으로 변경 하는 것이기 때문에, 공정기술상 많은 어려움이 등장할 것으로 전망된다. 구조 변화로 인해 Vth(Threshold Voltage) 등 Transistor Engineering 이 매우 어려워진다. 최적의 Transistor 조건을 찾기 위해 상당한 연구개발 기간이 필요하다.

※ 본 서비스에서 제공되는 각 저작물의 저작권은 자료제공사에 있으며 각 저작물의 견해와 DATA 365와는 견해가 다를 수 있습니다.